电院来新泉教授团队首次在集成电路顶级国际期刊JSSC上发表一作论文

2018年6月,微电子学与集成电路领域国际顶级期刊《IEEE固态电路学报》(IEEE Journal of Solid-State Circuits,简称JSSC)登载了6165cc金沙总站检测中心来新泉教授团队以为西电第一作者单位发表的论文“Oversampling Successive Approximation Technique for MEMS Differential Capacitive Sensor”。该工作全部在西电完成,6165cc金沙总站检测中心的来新泉教授亲自指导的博士生钟龙杰为该论文第一作者,叶强、袁冰等老师提供了部分流片验证和测试。西电成为西北地区首个以第一作者单位身份发表JSSC论文的高校,充分展示了西电在集成电路设计领域深厚的积累和雄厚的科研实力。

JSSC为集成电路设计领域国际顶级学术期刊。自1966年创刊至今50余年时间内,中国大陆高校在此期刊上总计发表论文仅40余篇。其中,清华大学发表17篇,复旦大学发表10篇,电子科技大学发表5篇,东南大学4篇,北京大学3篇,哈尔滨工业大学与华中科技大学分别于2015年和2017年突破第一篇。

可点击下图查看全文↓

可点击上图查看全文 ↑

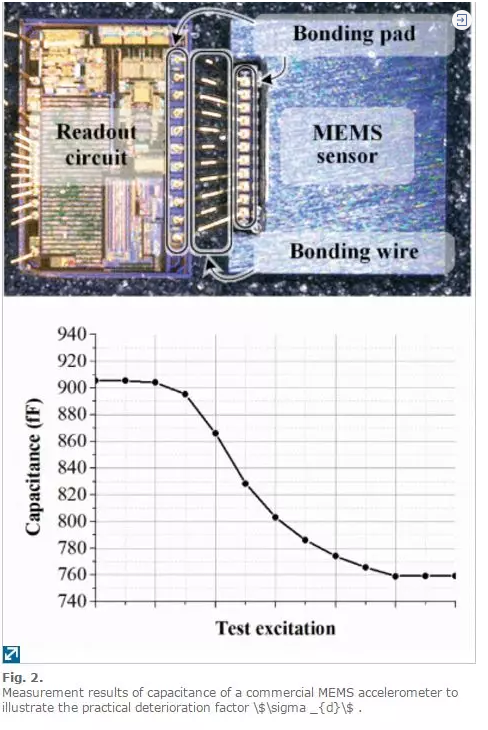

MEMS传感器是当前建设物联网生态系统关键的硬件技术之一,也是倍受商/军/工/学术界关心的重大建设方向。该研究围绕微米级MEMS工艺和纳米级CMOS工艺的尺寸缩微效应带来的设计挑战——包括寄生参数导致的增益误差恶化效应、噪声恶化效应、机电耦合导致的非线性调制效应等——全面展开。该研究的初步成果是针对寄生电容导致的恶化效应提出了一种迭代型读出方法,并采用一种精简的电路实现。结果极大改善亚飞法级MEMS梳齿电容型加速度计的读出精度。芯片采用0.18um BCD工艺制造,在0.35uW的功耗和1.8V的低电压条件下实现了-80dB PCRR的高寄生电容抑制比(领先国际同类研究水平14dB以上)。后续的已完成了5版流片验证,进一步达到了-124dB的寄生电容抑制比,系统性研究成果已陆续发表在电路领域旗舰期刊《IEEE Transactions on Circuits and Systems I: Regular Papers》上。并正积极在推进该研究成果入围顶级会议ISSCC,该研究极大推进了西电在集成电路领域的技术拓展与国际认可度。6165cc金沙总站检测中心来新泉教授团队还在《IEEE Transactions on Power Electronics》、《IEEE Transactions on Industrial Electronics》、《IET Power Electronics》等期刊上,于该领域发表多篇一作论文。